Informatique & Sciences du Numérique

Olivier SEBASTIEN ESIROI-STIM

oliviers[@]co.univ-reunion.fr

Ce cours est sous licence

Par Olivier SEBASTIEN et al, sauf cas particulier

Ce cours est mis à disposition selon les termes de la licence Creative Commons Paternité -Pas d’Utilisation Commerciale -Pas de Modification 3.0 non transcrit.

Ce cours vise à étudier quelle structure matérielle permet d'exécuter les programmes répondant à nos divers besoins. On se demandera également comment évaluer les performances d'une telle architecture.

Bien entendu, il sera difficile d'ignorer complètement les aspects logiciels : ils sont étroitement associés au matériel. Le logiciel de bas niveau qui se trouve à l'interface sera donc lui aussi évoqué.

Après un bref rappel sur le binaire, notre parcours commencera par une présentation globale et générique de l'architecture matérielle. Puis, nous nous focaliserons sur son « chef d'orchestre », le microprocesseur. Finalement, nous terminerons en faisant une initiation au langage le plus simple qui régisse cette architecture : l'assembleur.

Le binaire constitue le langage de base de notre architecture. On est donc à tout moment contraint à utiliser un alphabet constitué de deux lettres : 0 et 1.

Les circuits électroniques manipulent des courants électriques. Toute l'information plus complexe (image, son, …) doit, comme on l'a vu précédemment, être exprimée de cette manière.

On aurait pu définir un langage constitué d'une multitude de pas de tensions mais la précision des circuits, notamment dans les années 40, à l'aube des premiers ordinateurs, ne permettait pas une détection des changements de niveaux suffisamment fine. C'est pourquoi il a été décidé de se fonder sur une détection du niveau de courant plus simple : il y a du courant (état 1) ou il n'y en a pas (état 0).

L'entité élémentaire de stockage d'information est le bit, qui stock soit un état 1, soit un état

0. De là découlent des multiples et des variantes utilisées pour mesure la vitesse de

transmission des données. Le Kilobit: 1 kb = 210 = 1024 bits

Les unités de base sont complétées par une mesure en octets est plus courante. En effet, historiquement, un octet était la capacité mémoire requise pour stocker un caractère (lettre, chiffres, symboles) en ASCII. Le texte étant quasiment le seul type d'information manipulée à l'époque, on pouvait donc évaluer pratiquement la capacité d'un support.

On distingue plusieurs multiples :

Le Kilo-octet: 1 Ko = 210 = 1024 octets (KB en anglais) Le Mega-octet: 1 Mo = 220 octets = 210 Ko = 1024 Ko (MB en anglais)

Le Giga-octet: 1 Go = 230 octets = 210 Mo = 1024 Mo (GB en anglais)

Le Tera-octet : 1 To = 240 octets = 210 Go = 1024 Go (TB en anglais)

Le Peta-octet : 1 Po = 250 octets = 210 To = 1024 To (PB en anglais)

Remarque : la traduction anglaise de mot octet est byte. Toutefois, la confusion avec le bit est tout à fait possible lorsqu'on utilise les unités. C'est pourquoi, on respectera à la lettre la convention suivante : le bit est représenté par un b minuscule, le Byte par un B majuscule.

En décembre 1998, la Commission Electrotechnique Internationale (IEC) a adopté une nouvelle charte de nommage des unités de mesure de l'information informatique afin de l'harmoniser avec les autres unités du Système International (SI). En effet, dans ce système, le préfixe Kilo fait référence à un facteur 1000 alors qu'en informatique, le facteur est 1024, fondé sur la base 2.

Il a donc été créé un préfixe binaire utilisant les mêmes multiples. On parle donc de Kilo Binaire, de Mega Binaire, de Giga Binaire, … Deux sous-variantes existent, pour les bits et les octets.

| Nom SI | Symbole |

| Kibi | Ki |

| Mebi | Mi |

| Gibi | Gi |

| Tebi | Ti |

| Pebi | Pi |

Facteur

210 220 230 240 250

| Nom complet | Ancien préfixe |

| Kilobinaire | Kilo |

| Megabinaire | Mega |

| Gigabinaire | Giga |

| Terabinaire | Tera |

| Petabinaire | Peta |

Nom SI (anglais entre parenthèses)

Kibibit Kilobit Mebibit Megabit Mebioctet (MebiByte) Megaoctet (MegaByte) Gibioctet (GibiByte) Gigaoctet (GigaByte) Pebioctet (PebiByte) Petaoctet (PetaByte)

Abréviation 1 Kib = 210 bit = 1024 bit 1 Kb = 103 bit = 1000 bit

1 Mib = 220 bit 1 Mb = 106 bit 1 Mio = 1 MiB = 220 octets = 1048576 bit 1 Mo = 1 MB = 106 octets = 1000000 octets 1 Gio = 1 GiB = 230 octets 1 Go = 1 GB = 109 octets 1 Pio = 1 PiB = 240 octets 1 Po = 1 PB = 1012 octets

Tableau 2.2 : quelques unités standards de représentation de l'information binaire

Manipuler les unités de mesure de l'information et faire le lien avec des faits rencontrés dans la réalité.

Calculatrice intégrée à tout système d'exploitation.

Cet exercice est basé sur la réflexion. La stratégie consiste à comparer deux valeurs : l'une théorique, l'autre pratique.

La capacité réelle d'un disque dur de 500 Go est de 465 Go. Expliquer ce fait. Y a-t-il tromperie sur la marchandise ?

Manipuler les unités de mesure de l'information et faire le lien avec des faits rencontrés dans la réalité.

Approcher un des principes du stockage d'information sur un disque numérique.

Calculatrice intégrée à tout système d'exploitation.

Cet exercice est basé sur la réflexion. Toutefois, il peut être nécessaire de revoir le principe de l'échantillonnage vu dans le cours précédent.

En audionumérique grand public, les spécifications du CD audio prévoient fs = 44,1 KHz avec une quantification q = 16 bits en stéréo. A partir de ces données, il est possible de calculer la consommation mémoire par minute de son : 10,09 Mo.

La structure présentée ici est valable pour l'immense majorité des systèmes existants : on pense bien sûr aux micro-ordinateurs, mais tout autre système numérique est bâti sur les mêmes principes : lecteur DVD/Bluray, console de jeux, téléphone portable, synthétiseur, montre, ...

Le principe de l'architecture informatique remonte aux années 40-50, même encore actuellement. L'idée globale est la suivante : le système peut exécuter un nombre indéfini d'actions, à partir des mêmes composants. On appelle programme l'élément qui implémente une action que doit accomplir ce système. On reste bien sûr soumis aux capacités du matériel.

La grande originalité de ce concept est donc que l'on peut faire accomplir à une telle machine, appelée ordinateur, des tâches qui n'ont pas été pré-programmées par son fabricant, par opposition au concept d'automate.

Une architecture informatique comporte obligatoirement les catégories de fonctions suivantes :

Un circuit de traitement : il réalise les opérations nécessaires à l'accomplissement d'un programme. C'est ce qu'on appelle le microprocesseur (ou processeur), du nom du composant qui de nos jours intègre ce rôle autrefois dévolu à plusieurs composants

De la mémoire RAM (Random Access Memory) : c'est la zone de travail du microprocesseur. Une donnée et l'instruction qui intervient dessus doivent être transférées dans la mémoire pour que le traitement opère. Cette mémoire est volatile, c'est-à-dire que son contenu est perdu lorsque l'électricité est coupée

Des périphériques d'entrée/sortie (I/O en anglais, pour input/output) : cette catégorie recouvre de multiples rôles :

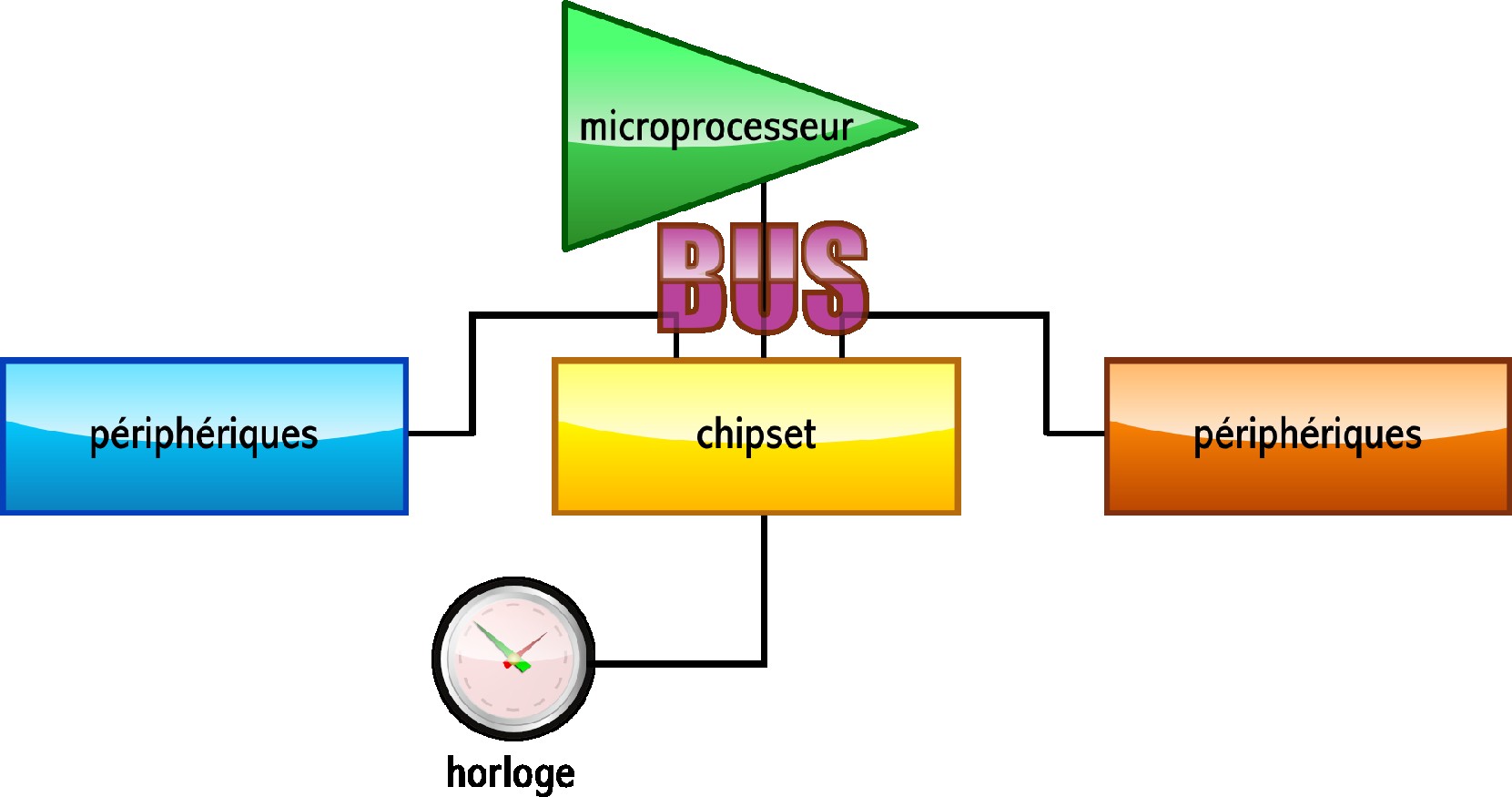

Tous ces circuits communiquent entre eux par l'intermédiaire de voies appelées bus à la cadence donnée par une horloge.

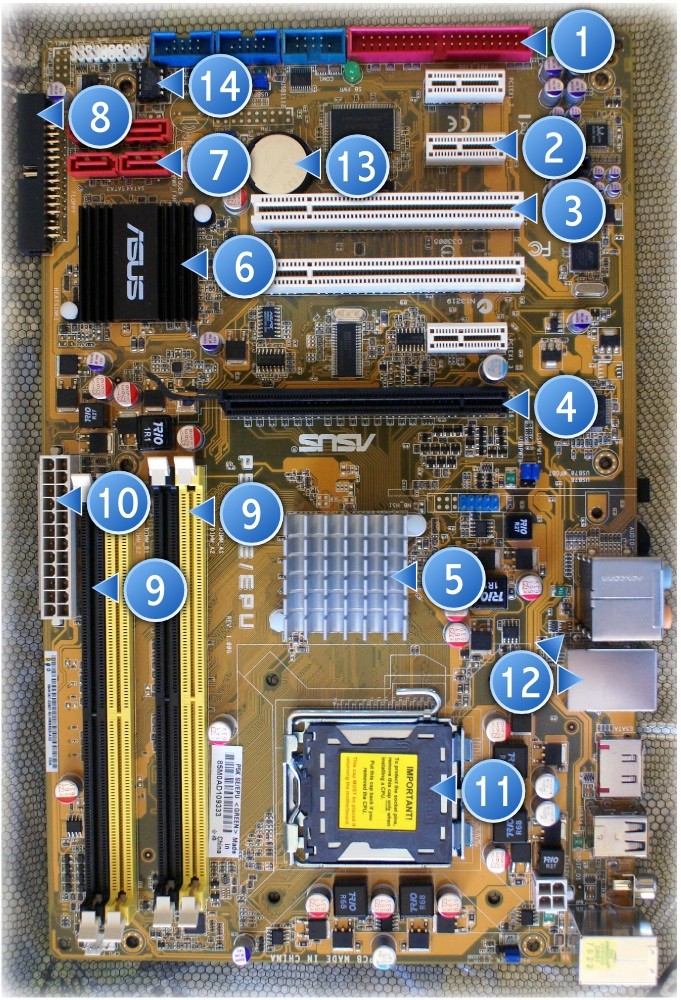

Physiquement, la plupart prend place aujourd'hui sur une carte mère, concentrant beaucoup de rôles.

Pour assurer le fonctionnement de l'architecture, un contrôle permanent doit être effectué afin d'organiser les échanges entre composants. Autrefois, il était assuré par un jeu de puces différentes. Les progrès techniques ont permis l'intégration de ces fonctions au sein d'un ensemble central appelé chipset (littéralement « jeu de puces »). C'est lui qui assure la régulation des flux et l'accès du processeur aux autres ressources.

Physiquement, sur les ordinateurs traditionnels, les chipsets actuels sont composés de deux parties :

Northbridge (encore appelé SPP) : il gère principalement la mémoire, le système graphique et la liaison au Southbridge

Southbridge (encore appelé MCP) : il gère les ports d'entrée/sortie (PCI, USB, …), l'alimentation (passage en veille) et le signal de l'horloge

Sur les équipement mobiles, le chipset est un seul composant et peut même être intégré au processeur.

L'imbrication entre les différents éléments vus précédemment est présenté sur l'' Illustration

L'horloge rythme les échanges et traitements de l'architecture. Elle produit des « tops » déclenchant ces événements. Il est ainsi possible d'exprimer la vitesse, en Hertz (Hz) de chaque composant comme un multiple de la pulsation de base que donne l'horloge. Actuellement, elles varient de l'ordre de la centaine de mégahertz (MHz) dans les systèmes embarqués et sur certains composants des cartes mère à quelques gigahertz (GHz) dans les microprocesseurs et les cartes graphiques.

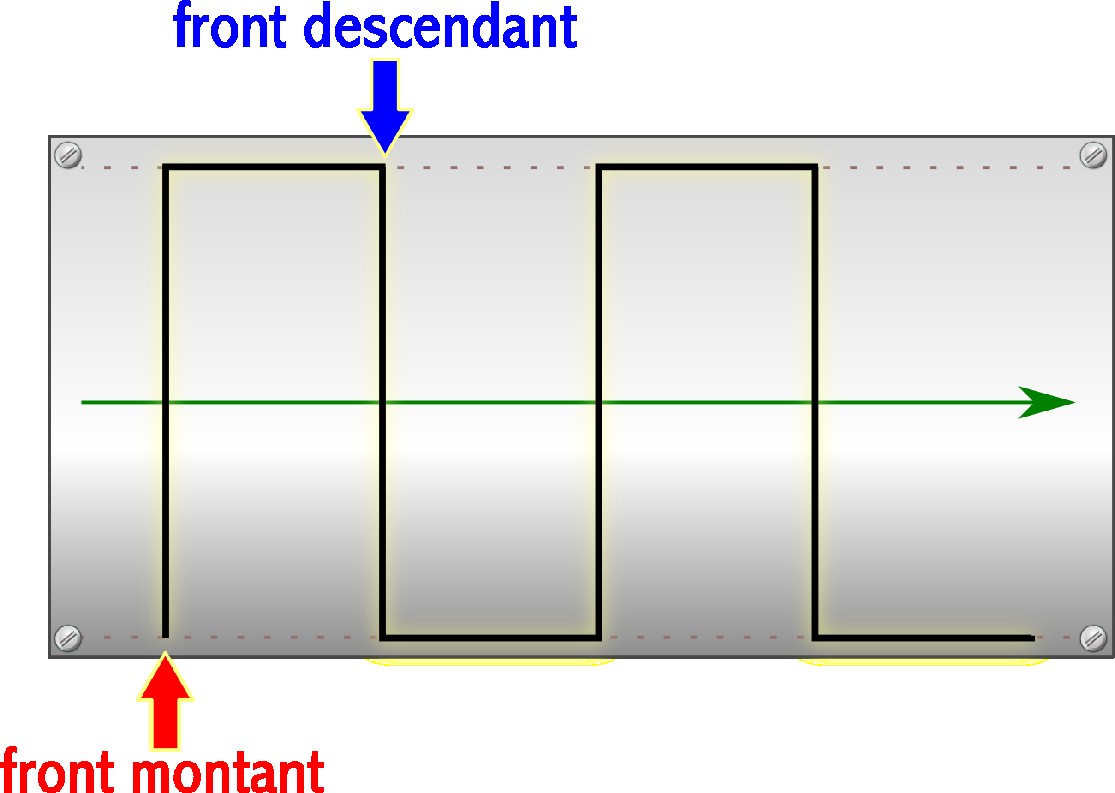

Techniquement, il s'agit d'un quartz qui oscille lorsqu'il est traversé par un courant. Le signal produit est une forme d'onde carrée, visualisée à l 'Illustration 3.2.

Initialement, c'était le front montant de l'horloge qui est utilisé pour déclencher les opérations et les échanges. A l'heure actuelle, le front descendant est aussi utilisé pour doubler (théoriquement) la quantité d'information échangée par cycle. On a ainsi deux modes :

SDR : Single Data Rate : transfert normal reposant uniquement sur les fronts montants

DDR : Double Data Rate : transfert doublé utilisant fronts montants et descendants, on a donc deux échanges par période au lieu d'une

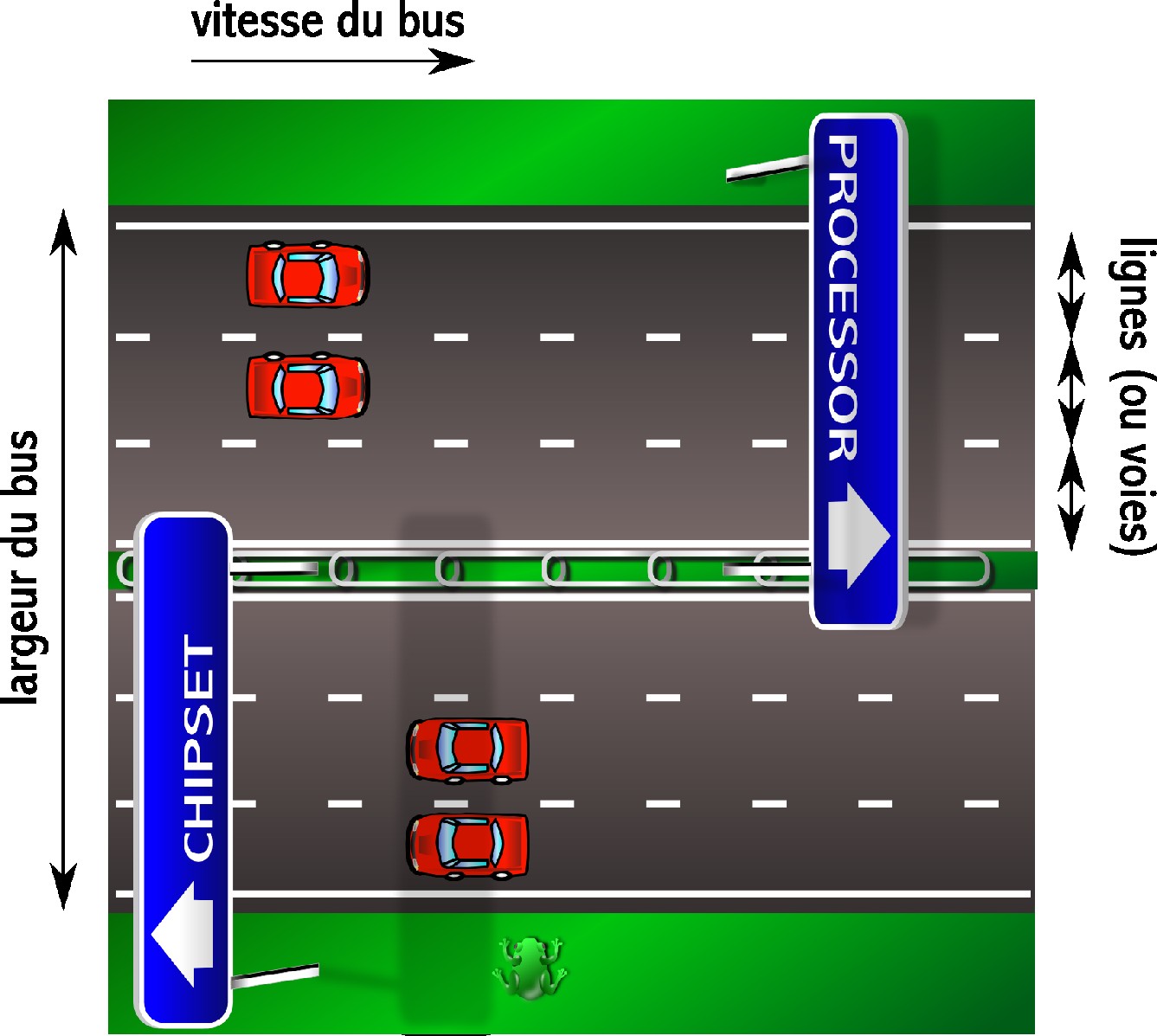

Comme on l'a vu précédemment, le bus est la voie d'interconnexion des composants. Il se décompose en deux parties : le bus d'adresse (address bus), qui donne la destination des données le bus de données (data bus) qui contient l'information elle-même. Le bus principal d'une architecture, celui qui interconnecte le microprocesseur, la mémoire et le chipset est le FSB (Front Side Bus). Plus généralement, les bus sont gérés par des contrôleurs et peuvent être reliés entre eux par des ponts.

Un bus est défini par les caractéristiques suivantes : sa largeur en bits, ce qui induit deux grandes familles de bus

sa vitesse, en MHz

sa directionnalité :

son type : SDR ou DDR. Dans ce dernier cas, il existe des variantes aux apports plus ou moins réels. On peut noter le cas du DDR2 qui utilise fronts montants et descendants simultanément pour une lecture de donnée et une écriture ce qui double encore le débit par rapport au DDR et donc le quadruple par rapport au SDR. Du moins théoriquement, car dans la pratique, on conçoit aisément qu'il faut être prêt à faire les lectures et écritures simultanées à chaque cycle, ce qui est rarement le cas

L 'Illustration 3.3 propose un parallèle avec une autoroute pour évoquer la plupart de ces caractéristiques. Les voitures représentent les bits d'information.

Dans la pratique, les caractéristiques techniques d'un bus peuvent souvent être assimilées à sa bande passante, c'est-à-dire la quantité d'information pouvant être transférée par seconde. Le plus souvent, sa valeur maximale théorique est calculable grâce à la formule suivante : B =T × L × f

où B : bande passante en bits/s

Étant données les valeurs actuelles, on a souvent l'habitude de convertir la bande passante en Mo/s ou en Go/s. Pour cela, on divise d'abord la valeur calculée par la formule ci-dessus par 8 (pour obtenir des octets) puis un certain nombre de fois par 1024.

Remarque : par définition, il n'est pas possible d'utiliser la formule précédente pour certains bus, par exemple si celui-ci propose un système de compression des données. En effet, dans ce cas, le taux de compression dépend du type de données.

Visualiser les différentes fonctions de l'architecture matérielle sur deux systèmes numériques de la vie courante.

Aucun

L'idée est de décomposer chaque équipement par rapport à son usage : que produit-il ? Comment le manipule-t-on ?

On considère les deux équipements suivants.

Équipement 1 Équipement 2 Donner pour chacun d'eux la liste de leurs périphériques d'entrées/sorties.

Déterminer les performances d'un bus à travers sa bande passante.

Calculatrice intégrée à tout système.

Il suffit d'appliquer la formule.

Calculer la bande passante du bus mémoire d'un circuit graphique possédant les caractéristiques suivantes : 128 bits DDR @500 MHz.

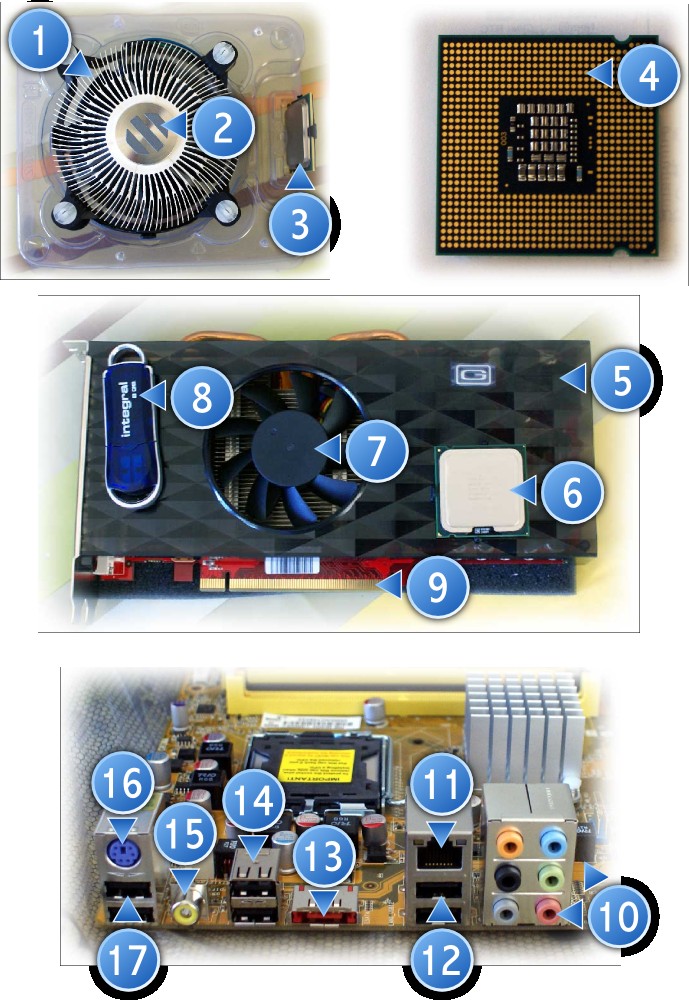

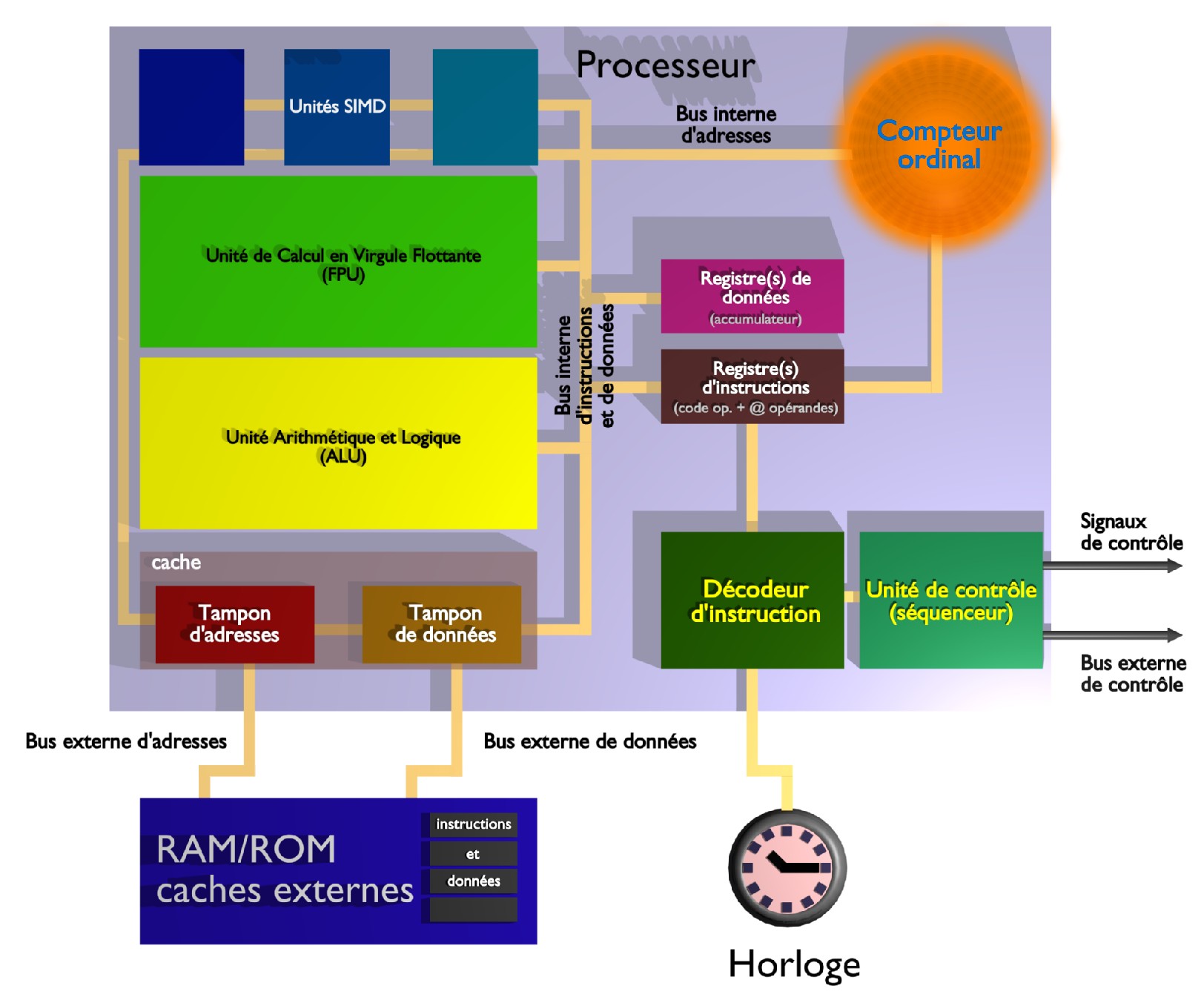

Appréhender les principaux composants d'un ordinateur.

Aucun

Pas de stratégie particulière.

Voici les photographies d'une carte mère et de divers composants. Donner les nom des pièces repérés par les numéros et expliquer leur rôle.

Dans l'architecture matérielle telle que présentée précédemment, le microprocesseur joue un rôle clé car c'est lui qui accomplit le travail demandé. Même si au fil des années il s'est vu adjoindre de nombreux circuits pour le décharger de certaines tâches, c'est lui qui dirige les opérations, agissant comme un chef d'orchestre avec ses musiciens.

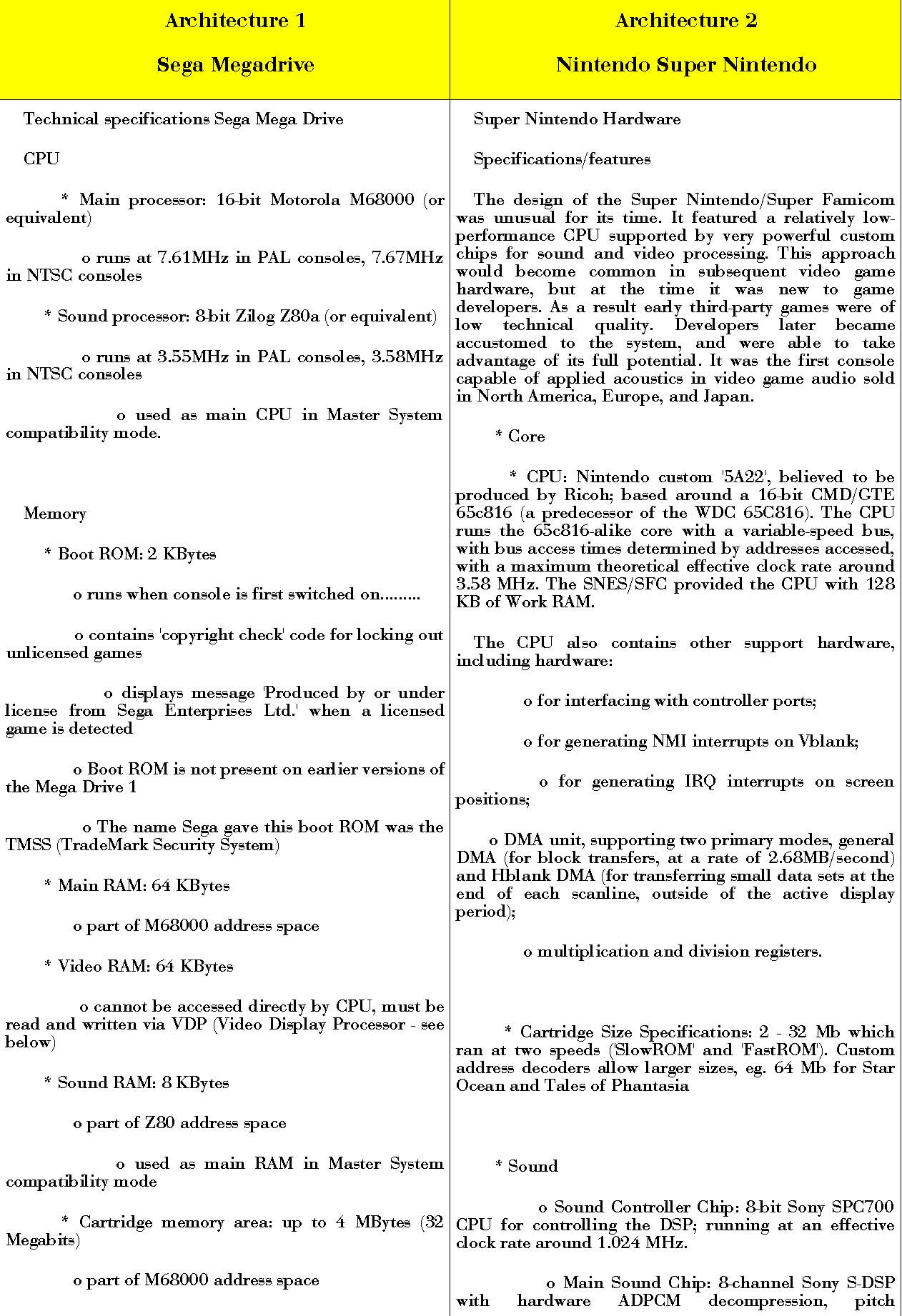

Le processeur est composé des unités fondamentales suivantes, représentées à l 'Illustration

4.1 : Des registres : mémoires très rapides contenant

◦ les données à traiter : registres de données

◦ les instructions : registre d'instruction Il existe plusieurs types de registres. Les plus utilisés sont les registres généraux, nommés dans l'architecture des PC EAX, EBX, ECX, EDX, ESI et EDI Une unité de commande qui contrôle le travail à accomplir et les cycles Un compteur ordinal qui contient l'adresse mémoire de la prochaine instruction à exécuter Des tampons (buffers) stockant temporairement les données et/ou instructions afin d'éviter des accès à la mémoire hors processeur (RAM/ROM/Mémoire cache externe), plus lents, pour les éléments utilisés fréquemment D'un décodeur d'instruction qui paramètre le registre d'instruction

Des unités de traitement : ce sont elles qui font les calculs à proprement dit. On compte en particulier :

Toutes ces unités sont reliées entre elles par des bus pouvant être dédiés au transport de données, d'instructions ou d'adresses. L'accès aux différentes mémoires externes se fait aussi par des bus externes de données et d'adresses.

Enfin, le processeur dispose de deux liaisons vers l'environnement extérieur : un bus externe de contrôle et une ligne de signaux de contrôle afin de communiquer avec le chipset (et donc le reste des composants).

Il existe beaucoup d'autres unités spécifiques à certains types de processeurs particuliers ou dont l'équipement varie en fonction des progrès technologiques.

Comparer deux architectures différentes conçues pour répondre au même objectif.

Aucun

Il faut d'abord identifier les critères qui seront utilisés pour définir les performances. Exemple : processeur, mémoire... Ensuite, on pourra remplir un tableau avec dans chaque colonne l'une et l'autre des architectures.

Le but de cet exercice est de comparer deux architectures dédiées au même but : le jeu vidéo. Pour cela, une documentation est fournie ci-dessous.

Technical specifications Sega Mega Drive CPU

* Main processor: 16-bit Motorola M68000 (or equivalent)

Memory

* Boot ROM: 2 KBytes

o runs when console is first switched on.........

* Cartridge memory area: up to 4 MBytes (32 Megabits)

o part of M68000 address space Super Nintendo Hardware

Specifications/features

The design of the Super Nintendo/Super Famicom was unusual for its time. It featured a relatively lowperformance CPU supported by very powerful custom chips for sound and video processing. This approach would become common in subsequent video game hardware, but at the time it was new to game developers. As a result early third-party games were of low technical quality. Developers later became accustomed to the system, and were able to take advantage of its full potential. It was the first console capable of applied acoustics in video game audio sold in North America, Europe, and Japan.

* Core

* CPU: Nintendo custom '5A22', believed to be produced by Ricoh; based around a 16-bit CMD/GTE 65c816 (a predecessor of the WDC 65C816). The CPU runs the 65c816-alike core with a variable-speed bus, with bus access times determined by addresses accessed, with a maximum theoretical effective clock rate around

3.58 MHz. The SNES/SFC provided the CPU with 128 KB of Work RAM.

The CPU also contains other support hardware, including hardware:

o multiplication and division registers.

* Cartridge Size Specifications: 2 -32 Mb which ran at two speeds ('SlowROM' and 'FastROM'). Custom address decoders allow larger sizes, eg. 64 Mb for Star Ocean and Tales of Phantasia

* Sound

o Game cartridges larger than 4 MBytes must use bank switching

Graphics

The Mega Drive has a dedicated VDP (Video Display Processor) for playfield and sprite control. This is an improved version of the Sega Master System VDP, which in turn is derived from the Texas Instruments TMS9918.

* Pixel resolution: depends on display mode

o interlaced modes can provide double the vertical resolution (i.e. 320x448 for NTSC). Used in Sonic 2 for 2-player split screen

Sound

o 3 sound generators, 4 octaves each, 1 white noise generator

Inputs and outputs

* RF output: connects to TV aerial input

o exists on European and Asian Mega Drive 1 only

o other models must use external RF modulator which plugs into A/V output

* A/V output: DIN connector with composite video, RGB, and audio outputs

o Mega Drive 1 has 8-pin socket (same as Master System), supports mono audio only

modulation, echo effect with feedback (for reverberation) with 8-tap FIR filter, and ADSR and 'GAIN' (discretely controlled) volume envelopes.

o Memory Cycle Time: 279 Minutes

o Effects

# Pixelization (mosaic) per background

o Mega Drive 2, Multimega, and other models have 9-pin mini DIN socket with both mono and stereo audio

o exists on all Japanese and Asian Mega Drive 1 units, and on early European Mega Drive 1 units

# Color addition and subtraction # Clipping windows (per background, affecting color,

math, or both) # Scrolling per 8x8 tile # Mode 7 matrix operation

* Power Adapter

o Transformer Input: 120 VAC, 60 Hz, 17 watts

o Transformer Output: 10 VDC, 850 mA (NTSC), 9 VAC (PAL)

* Plugs

Découvrir les caractéristiques d'un ordinateur sans l'ouvrir.

A chercher !

Il existe des logiciels et des manipulations permettant de connaître les principales caractéristiques techniques d'un ordinateur. Quelques recherches sur Internet permettront de trouver des idées adaptées au système d'exploitation (Windows, Mac, Linux) de la machine en présence.

Déterminer les caractéristiques de processeur, de mémoire, de disque et de ports d'entrée/sortie de l'ordinateur en face de vous.

Nous terminerons ce cours en analysant comment fonctionne la communication et la programmation de bas niveau dans l'architecture

Conceptuellement, tous les circuits de l'architecture sont conçus pour réagir à des sollicitations électriques. On distingue les instructions, qui déclenchent des fonctions et les données, qui sont l'information sur laquelle les fonctions seront appliquées.

Le but de ce chapitre est de passer en revue quelques commandes qui utilisent le microprocesseur pour commander des périphériques d'entrée-sortie.

Le fonctionnement de l'architecture est organisé en cycles réguliers. Le travail à accomplir à chaque pas de temps ne peut toutefois pas tout le temps être anticipé dans la liste des instructions. D'où l'implémentation d'un mécanisme d'interruptions qui permet d'interrompre les tâches courantes du processeur afin d'exécuter des tâches plus « urgentes » ou en rapport avec l’occurrence d'événements spéciaux comme par exemple le dépassement d'une valeur seuil, la notification d'un périphérique qui a terminé son traitement et qui en attend un autre, la sollicitation d'un contrôleur, …

Il existe deux types d'interruptions :

matérielles: utilisées par les unités d'entrée/sortie

logicielles: servant à appeler des routines du BIOS, logiciel le plus simple d'un ordinateur ou du système d'exploitation

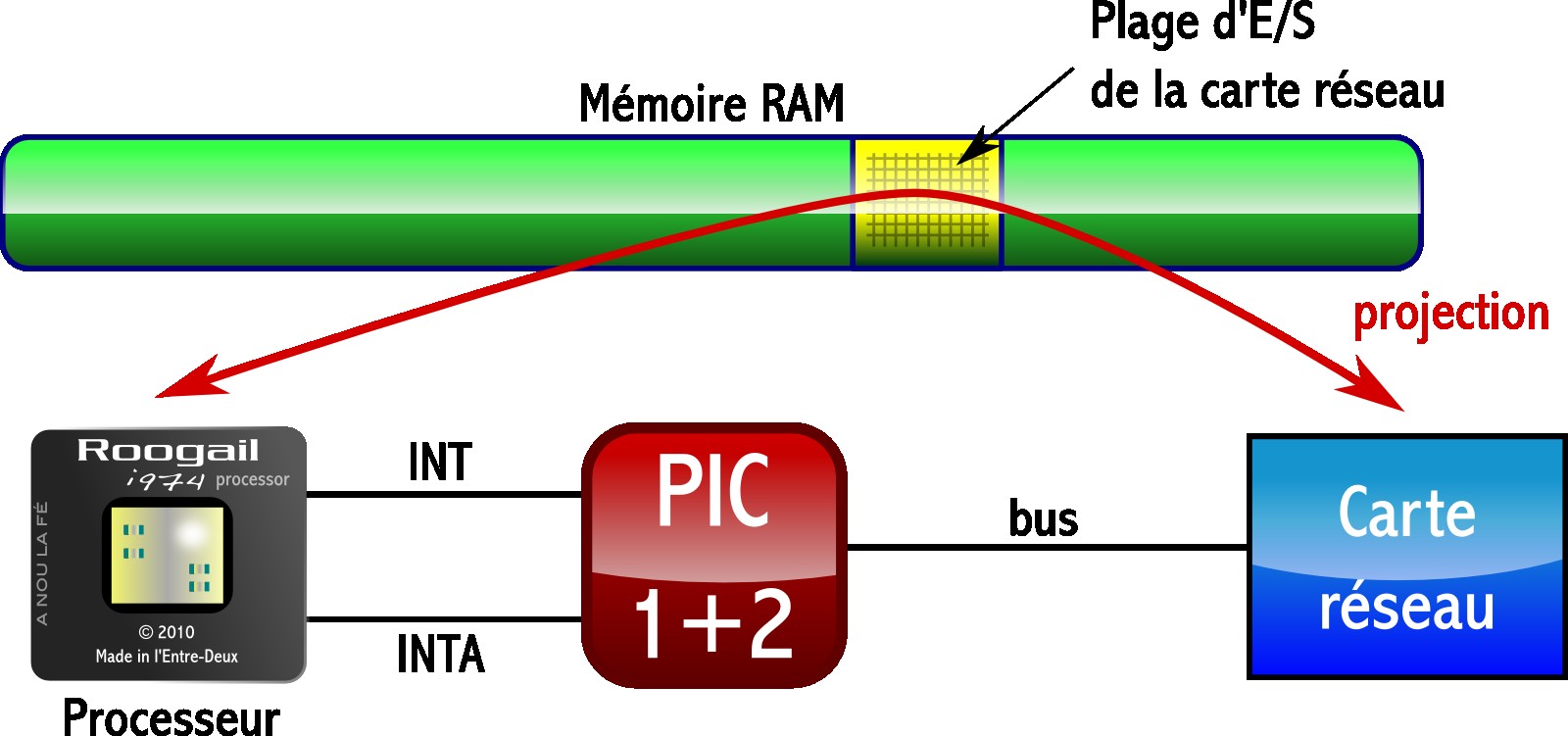

Il convient à présent d'étudier comment le processeur peut communiquer avec les périphériques, à travers ce dispositif et par l'intermédiaire du chipset.

Toutes les unités ont une adresse propre, un port d'E/S en mémoire RAM, pour réaliser les échanges de données. C'est ce qu'on appelle la projection mémoire des E/S (I/O memory mapping). Ainsi, le processeur s'adresse à cette adresse pour atteindre l'unité en question, en lecture et/ou écriture.

216

Sur les PC, ordinateur historiquement 16 bits, il y a adresses possibles pour cette projection.

Exemple : fonctionnement d'une carte réseau (Illustration 5.3)

Une portion de la mémoire RAM est dédiée, de façon logicielle ou matérielle (en déplaçant des cavaliers sur la carte) à la carte réseau. La moitié pour lire les données reçues, l'autre moitié pour envoyer des données.

Du point de vue du processeur, il suffit donc d'aller lire les données localisées aux adresses de réception de la projection mémoire pour accéder à ce que la carte réseau a transporté en entrée. La carte réseau, de son côté, ira chercher les données à expédier sur le réseau dans la plage d'adresses réservée aux données en sortie.

Le circuit PIC (Programmable Interruption Controller) se charge de gérer les interruptions.

Ce mécanisme permet des subtilités intéressantes, comme le partage de la mémoire RAM centrale aux périphériques. Exemples: carte graphique à mémoire partagée, chargement de samples dans les cartes son avancées, RAMdisks...

Avant de définir l'assembleur, il convient de présenter le langage machine. C'est le langage que le microprocesseur est capable de comprendre sans « traduction ». Concrètement, il s'agit d'une suite de 0 et de 1 qui représentent soit des ordres (instructions) soit des informations à traiter (données).

Voici un exemple d'opération en langage machine : A1 01 10 03 06 01 12 A3 01 14

On peut voir aisément qu'il s'agit de l'addition du contenu de deux adresses mémoire et du stockage du résultat dans une troisième adresse mémoire (ironie inside). Toutefois, certaines personnes éprouvent du mal à lire ce genre de code, c'est pourquoi il a été nécessaire d'imaginer une couche d'abstraction qui facilite l'écriture et la lecture d'un programme, sans trop s'éloigner du langage machine : l'assembleur.

L'assembleur est le langage le plus proche du langage machine car les opérations qui sont décrites dans un tel programme peuvent être interprétées directement par les différentes unités du processeur.

Pour des raisons de commodité et de lisibilité, les instructions sont représentées par des mots-clés plus faciles à manipuler par les humains. Les données peuvent quant à elles se voir représentées par des labels, des noms choisis par le développeur.

Les mots clés sont appelés mnémoniques. Ils forment la représentation symbolique et permettent de séparer les opérateurs des opérandes.

Exemple : l'addition donnée au paragraphe précédent peut s'écrire de la façon suivante en assembleur :

ADD @A, @B, @C

Concevoir et exécuter un programme en assembleur. Découvrir « l'envers du décor ».

Nasm et ld : ce sont des programmes basiques (en ligne de commande) mais puissants pour programmer en assembleur.

Un code de base est fourni. L'idée consiste à voir d'abord les différentes sections du programme puis à comprendre, à l'intérieur, à quoi sert chaque instruction.

On donne le code assembleur suivant :

| section .data | |

|---|---|

| hello: | db 'Hello world!',10 |

| helloLen: | equ $-hello |

| section .text | |

global _start

_start:

; Write 'Hello world!' to the screen mov eax,4 ; 'write' system call mov ebx,1 ; file descriptor 1 = screen mov ecx,hello ; string to write mov edx,helloLen ; length of string to write int 80h ; call the kernel

; Terminate program mov eax,1 ; 'exit' system call mov ebx,0 ; exit with error code 0 int 80h ; call the kernel

Code extrait du cours d'Assembleur de Derick Swanepoel © 2002

Découvrir des interruptions utilisées dans la gestion des fichiers dans une architecture matérielle.

Nasm et ld : comme à l'exercice précédent.

Un code de base est aussi fourni. Il suffira de l'adapter au contexte. Il y a ici une nouveauté : des informations fournies par l'utilisateur sont récupérées grâce à une pile.

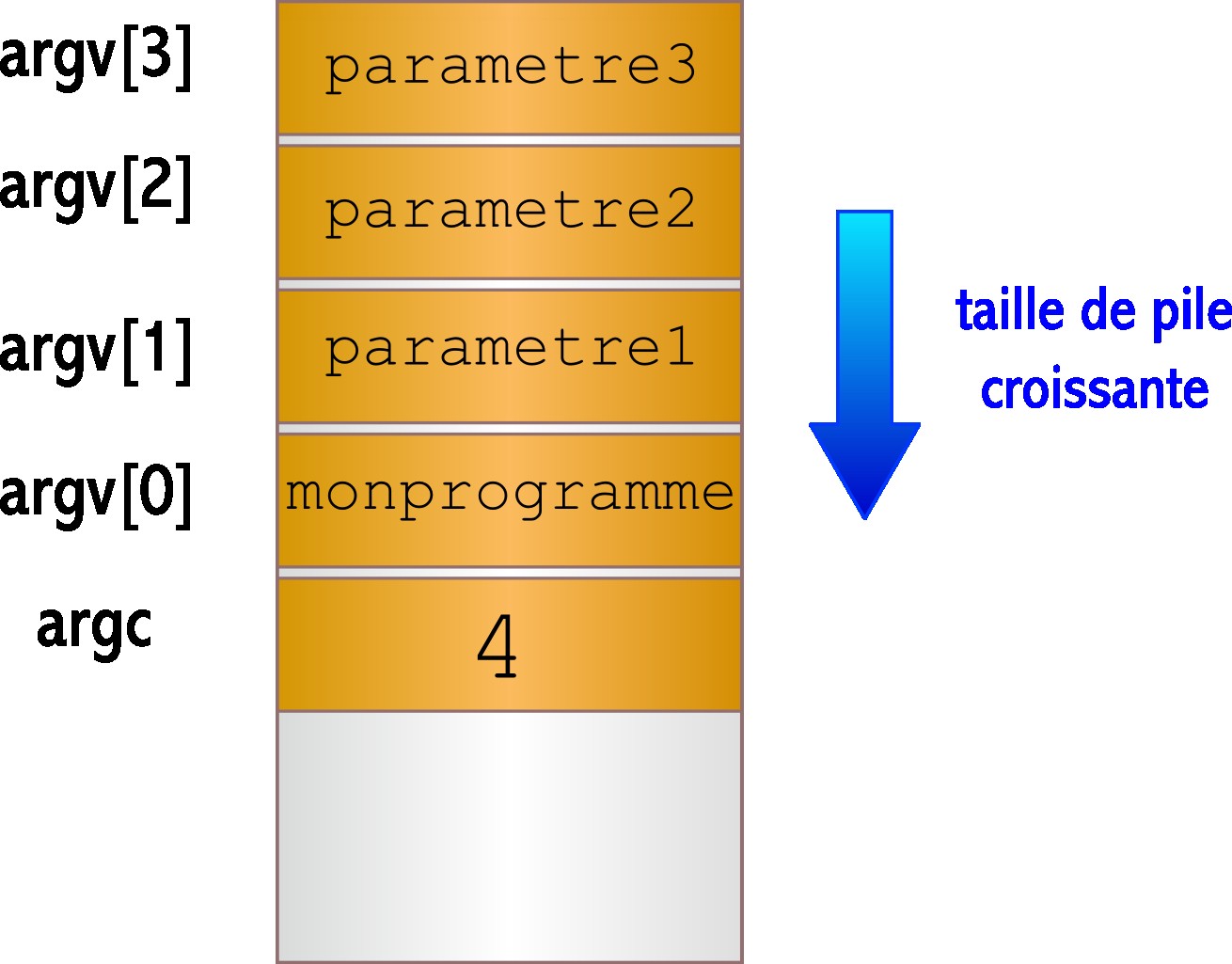

La pile (stack en anglais) est une structure d'organisation des données : c'est un espace mémoire réservé à l'enregistrement continu de données.

Pour l'expliquer, on peut tout à fait prendre la métaphore de la pile d'assiettes dans l'évier, comme montré à l 'Illustration 5.2.

L'instruction assembleur PUSH permet de mettre une information au sommet de la pile, alors que l'instruction POP permet de la retirer.

Dans la structure de pile, c'est la dernière donnée à être entrée qui est la première à être accessible. On dit alors que c'est une structure de type LIFO : Last In First Out.

L'inverse de ce concept est le FIFO : First In First Out. Autrement dit, le premier arrivé est le premier servi. C'est le cas de la file d'attente à une caisse de supermarché.

Dans l'environnement que nous utilisons un mécanisme très pratique permet de récupérer dans la pile les paramètres que l'utilisateur a entré lors du lancement du programme.

Tout part de la ligne de commande qui lance le programme. Après le nom de celui-ci sont passés les différents paramètres séparés chacun par un espace.

Exemple : ./monprogramme parametre1 parametre2 parametre3

Tous ces éléments sont automatiquement placés sur la pile, dans cet ordre. Chacun d'eux est un argument (arg[n]), y compris le nom du programme qui est l'argument 0. Le nombre total d'arguments (argc) les précède dans la pile.

La structure de la pile au démarrage sera conforme à l 'Illustration 5.3.

Écrire et exécuter le programme donné ci-dessous

| section .data hello helloLen | db equ | $ | 'Hello, world!',10- hello | ; Our dear string; Length of our dear string | ||

|---|---|---|---|---|---|---|

| section .text global _sta | rt | |||||

| _start: | pop ebx pop ebx pop ebx | ; argc (argument count); argv[0] (argument 0, the program name); The first real arg, a filename | ||||

| mov | eax,8 | ; The syscall number for creat();(we already have the filename in ebx) | ||||

mov ecx,00644Q ; Read/write permissions in octal (rw_rw_rw_) int 80h ; Call the kernel ; Now we have a file descriptor in eax

test eax,eax ; Lets make sure the file descriptor is valid

js skipWrite ; If the file descriptor has the sign flag ;(which means it's less than 0) there was an ;oops, so skip the writing. Otherwise call the

;filewrite "procedure" call fileWrite

skipWrite: mov ebx,eax ; If there was an error, save the errno in ebx mov eax,1 ; Put the exit syscall number in eax int 80h ; Bail out

; proc fileWrite - write a string to a file

fileWrite: mov ebx,eax ; sys_creat returned file descriptor into eax, ; now move into ebx mov eax,4 ; sys_write

; ebx is already set up mov ecx,hello ; We are putting the ADDRESS of hello in ecx mov edx,helloLen ; This is the VALUE of helloLen because

; it's a constant (defined with equ) int 80h

mov eax,6 ; sys_close, ebx already contains file descriptor int 80h ret

; endp fileWrite

Code extrait du cours d'Assembleur de Derick Swanepoel © 2002